Exercise 7.5 Stability and phase marging

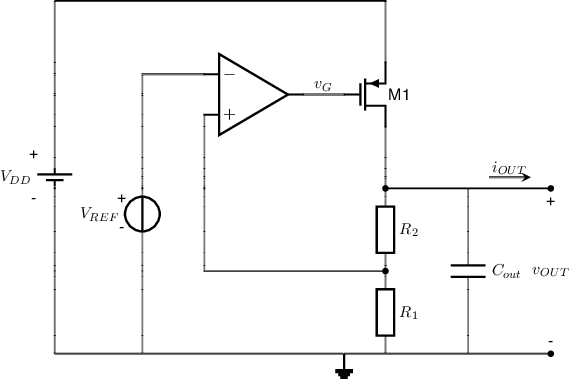

To build a stabilized power supply we may use the circuit below to regulate

down to

. We

assume

works in saturation and that this transistor has infinite output resistance.

-

a)

- To analyze the basic functionality of the circuit, at first we assume the opamp is ideal: ,

,

.

For this situation, derive an expression for .

For non-ideal opamps in feedback configurations, stability may be an issue. A more accurate

model of the opamp is having both finite gain and limited bandwidth, leading to an opamp gain

described by: .

This model is to be used for questions (b)-(d).

-

b)

- Derive an expression for the unity-gain bandwidth of this opamp in [Hz]. You may assume that

.

-

c)

- Derive an expression for the small signal loop gain.

Now let’s assume that we dimension ,

,

and

in such a way that the unloaded regulator is stable and its loop has sufficient phase margin.

-

d)

- An external current source draws a positive DC output current

out of the regulator. How does this influence the phase margin? Illustrate with either an analytical

proof or with a Bode plot.