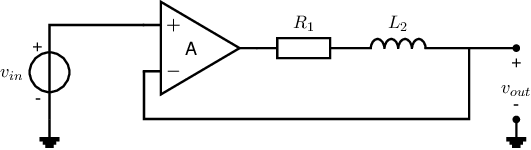

Exercise 7.4 Phase margins

Given is the circuit below. For the opamp, ,

, and the

voltage gain

is finite.

-

a)

- Derive an expression for the output impedance of the circuit (looking into the port denoted by

).

-

b)

- Draw the magnitude part of a bode plot of this output impedance. Indicate the values of the

poles/zeros (x-axis) and flat parts (y-axis).

It appears that the opamp in this circuit actually has a frequency dependent gain .

-

c)

- Show (with calculations and/or plots) that the phase margin is larger than

for the schematic above (with frequency dependent )

if the circuit is unloaded (if the load impedance is infinite).

-

d)

- Show (with calculations and plots) that the phase margin can go to very low values for the

schematic above (with frequency dependent )

if the circuit is loaded by a resistor

with unknown value.