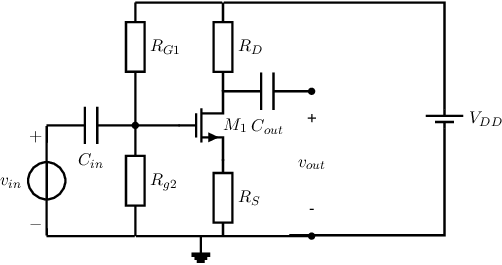

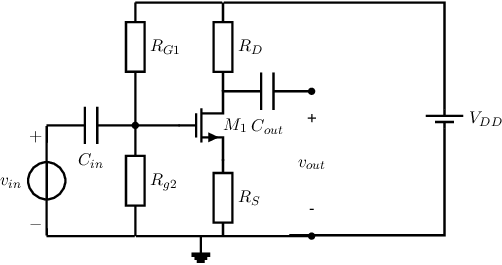

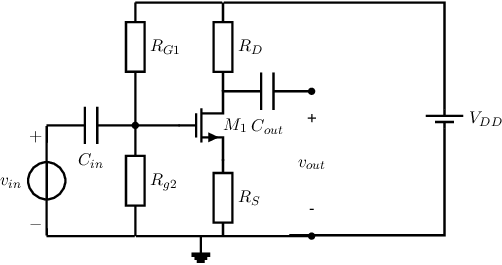

Exercise 3.8 Biasing an amplifier circuit with an NMOS transistor

Given is the amplifier circuit schematic below. The capacitors have an impedance that is negligible

at the signal frequency, nd the transistor is assumed to operate according to the square-law

().

-

a)

- We want to set .

Derive a (parametric) equation for the required value for

as a function of various component values and component properties.

-

b)

- For .

,

,

,

,

,

calculate the numerical value of the required .

Calculate the required value of .

-

c)

- To have some signal swing at the output and to have the transistor operating in saturation,

determine the allowed range for

values.

-

d)

- We want to increase the voltage gain of the amplifier. Does the gain get higher from putting a

capacitor parallel to ?

What about putting an inductor in series with ?

What about putting an inductor in series with ?

Note: this question is related to chapters 4 and 5.